El siliceno, un material semiconductor nuevo que combina las propiedades del silicio y el grafeno, se encuentra entre los candidatos más interesantes para su utilización en la fabricación de circuitería electrónica aún más pequeña que pueda integrarse en dispositivos inteligentes.

Con este material se está trabajando en proyecto de investigación europeo, en cuyo marco ya se ha dado un paso importante en la miniaturización de componentes nanoelectrónicos. El objetivo del proyecto era desarrollar dispositivos de futuro mucho más potentes y eficientes energéticamente.

Con este material se está trabajando en proyecto de investigación europeo, en cuyo marco ya se ha dado un paso importante en la miniaturización de componentes nanoelectrónicos. El objetivo del proyecto era desarrollar dispositivos de futuro mucho más potentes y eficientes energéticamente.

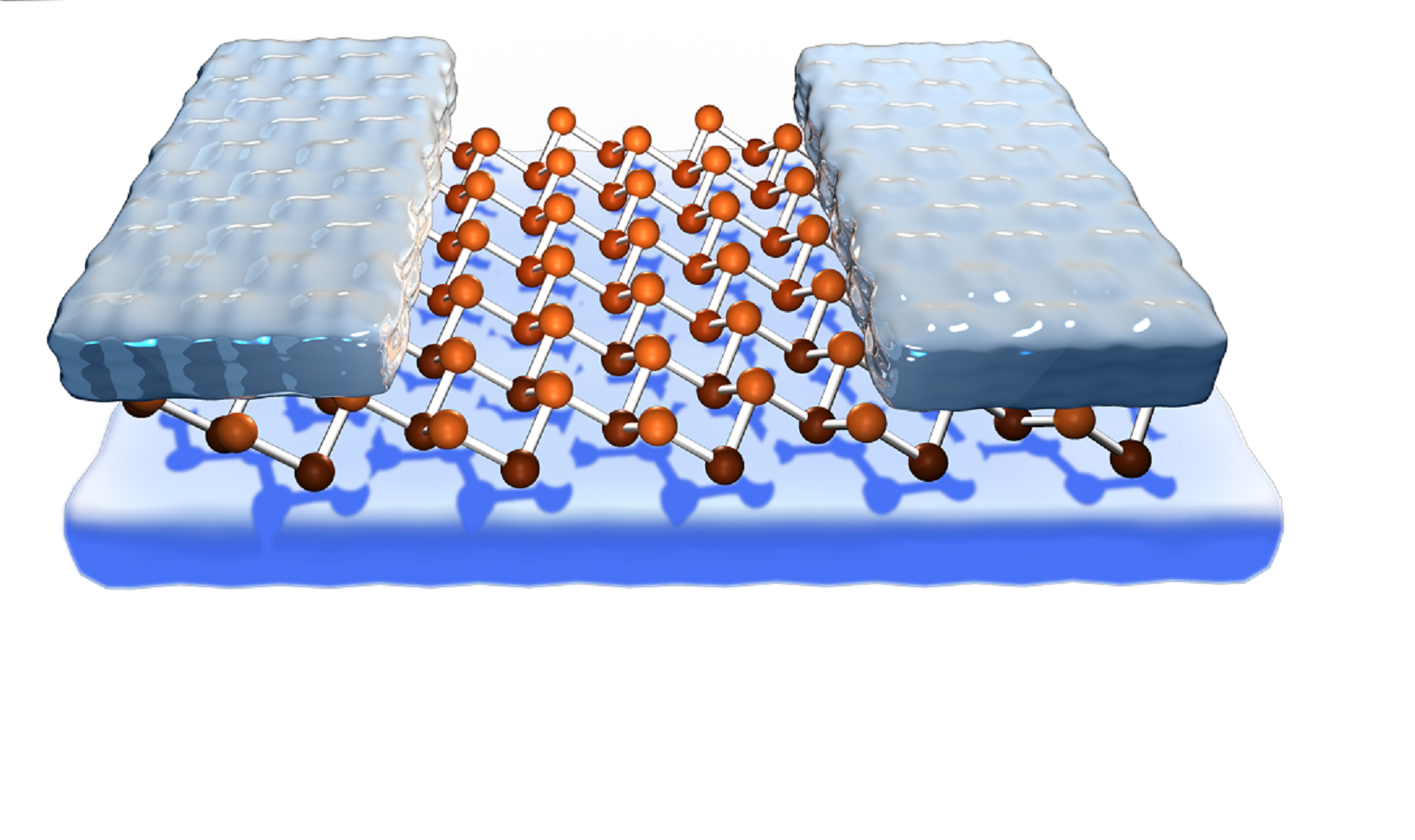

"Los componentes electrónicos se integran actualmente en capas múltiples de átomos de silicio. La integración de dichos componentes en una capa única permitiría reducir su tamaño de manera significativa y minimizar las fugas eléctricas, a la vez que se conseguiría aumentar la potencia y eficiencia energética de los dispositivos en los que se monten", explica el Dr. Athanasios Dimoulas, coordinador del proyecto, bautizado como 2D-NANOLATTICES , en un comunicado de la agencia Cordis.

Integración de componentes

El grafeno es una sustancia interesante puesto que se estructura en una única capa de átomos, aunque no posee el «vacío energético» necesario para ser material semiconductor.

El siliceno, variante bidimensional del silicio, aporta sus propiedades semiconductoras al mundo de los materiales 2D, si bien presenta el problema de que sus características se alteran al entrar en contacto con otras sustancias, por ejemplo metales.

La integración de componentes electrónicos en una capa única de siliceno manteniendo el rendimiento electrónico de éstos ha sido una tarea difícil para los investigadores, hasta ahora. El proyecto 2D-NANOLATTICES ha logrado un importante descubrimiento a nivel mundial al crear, a partir del material descrito, un transistor de efecto de campo (FET) capaz de funcionar a temperatura ambiente.

Los FET son un componente de conmutación fundamental en la circuitería electrónica, por lo que su integración en una capa única de átomos de silicio (con la estructura del siliceno) que —tras crecer en un sustrato de plata— se transfiere a otra capa formada por una sustancia más neutra, el dióxido de silicio, se considera un logro importantísimo.

"Las pruebas han demostrado que el rendimiento del siliceno es muy bueno en sustratos no metálicos", afirma con entusiasmo el Dr. Dimoulas, miembro de Demokritos, el Centro Nacional de Investigación Científica de Grecia.

"El hecho de tener este transistor, formado por una capa única de materiales como el silicio, es algo que no se había conseguido hasta ahora y que puede considerarse un gran avance, en virtud del cual podrían fabricarse transistores en dirección vertical con un tamaño cien veces menor", concluye el Dr. Dimoulas.

Veintinco veces más componentes electrónicos

De acuerdo con los cálculos del Dr. Dimoulas, la reducción vertical del tamaño del transistor en una capa única 2D formada por átomos permitirá reducir también las dimensiones lateralmente, lo que implicaría que la misma área del chip podría incorporar veinticinco veces más componentes electrónicos que antes.

Además, la utilización de un único canal estrecho para conducir la corriente eléctrica reduce las fugas de energía, problema que ha preocupado a los especialistas de semiconductores desde hace cierto tiempo: cómo reducir aún más el tamaño sin provocar un sobrecalentamiento de los dispositivos que provoque fugas eléctricas.

Éstas son buenas noticias para los fabricantes de chips, especialmente ahora que la carrera para fabricar la próxima generación de tecnologías de comunicación se hace más exigente, a raíz de la aparición de las redes móviles 5G.

El proyecto 2D NANOLATTICES, que transcurrió desde el 1 de junio de 2011 hasta el 31 de agosto de 2014, se financió con 1,63 millones de euros procedentes del 7PM (a través del programa Tecnologías futuras y emergentes) y contó con la participación de seis socios procedentes de cuatro países de la UE.

De acuerdo con los cálculos del Dr. Dimoulas, la reducción vertical del tamaño del transistor en una capa única 2D formada por átomos permitirá reducir también las dimensiones lateralmente, lo que implicaría que la misma área del chip podría incorporar veinticinco veces más componentes electrónicos que antes.

Además, la utilización de un único canal estrecho para conducir la corriente eléctrica reduce las fugas de energía, problema que ha preocupado a los especialistas de semiconductores desde hace cierto tiempo: cómo reducir aún más el tamaño sin provocar un sobrecalentamiento de los dispositivos que provoque fugas eléctricas.

Éstas son buenas noticias para los fabricantes de chips, especialmente ahora que la carrera para fabricar la próxima generación de tecnologías de comunicación se hace más exigente, a raíz de la aparición de las redes móviles 5G.

El proyecto 2D NANOLATTICES, que transcurrió desde el 1 de junio de 2011 hasta el 31 de agosto de 2014, se financió con 1,63 millones de euros procedentes del 7PM (a través del programa Tecnologías futuras y emergentes) y contó con la participación de seis socios procedentes de cuatro países de la UE.

Tendencias Científicas

Tendencias Científicas

Nuevo avance permitirá convertir el agua en combustible

Nuevo avance permitirá convertir el agua en combustible CIENCIA ON LINE

CIENCIA ON LINE